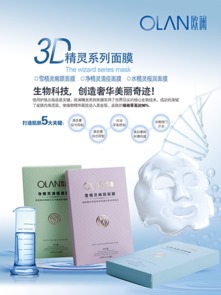

在追求卓越護膚體驗的征途中,歐瀾品牌始終致力于將前沿科技與自然精粹相融合。如今,我們滿懷欣喜地宣布,備受期待的歐瀾精靈系列生物科技面膜將于8月5日正式清新上市。這不僅是一次新品的發布,更是一場關于肌膚護理的科技革新。

一、 生物科技,定義護膚新維度

“生物科技”并非遙不可及的概念,歐瀾科研團隊將其精髓深度融入產品研發。本系列面膜的核心,在于運用了先進的生物發酵技術、細胞級修護成分及智能靶向滲透科技。我們篩選并培育特定有益微生物,通過精密可控的發酵過程,獲取高活性、小分子、易吸收的護膚成分。這些成分能夠更精準地作用于肌膚底層,促進細胞自我更新與修護,從源頭改善膚質,而非僅僅停留在表面滋潤。這標志著護膚從傳統的“外在覆蓋”邁向“內在煥新”的智能時代。

二、 精靈系列,開啟感官清新之旅

命名為“精靈”,寓意著產品如自然精靈般純凈、靈動且富有能量。此次上市的面膜,在配方與體驗上均體現了“清新”特質:

- 成分清新:嚴選天然植物精萃,結合生物科技轉化,確保成分的純凈與高效。無添加刺激性化學物質,溫和親膚,即使是敏感肌也能安心享受科技護膚的魅力。

- 膚感清新:獨創的天絲冰羽膜布,輕薄透氣如第二層肌膚。精華液質地清潤不粘膩,敷感清涼舒爽,能瞬間舒緩日間肌膚的緊繃與疲憊,仿佛為肌膚帶來一場酣暢淋漓的深呼吸。

- 香氛清新:調入了淡雅清新的天然植物香氣,在使用過程中營造出寧靜放松的感官體驗,讓護膚時刻成為每日的身心療愈儀式。

三、 卓越效能,見證肌膚煥變奇跡

歐瀾精靈系列生物科技面膜針對現代肌膚的多重需求,設計了多維度的護理方案(根據不同具體型號,功效側重或有不同),其主要效能包括:

- 深層修護,強化屏障:生物活性成分能深入修護受損的肌膚屏障,增強肌膚的鎖水力和抵御外界環境壓力的能力,使肌膚狀態更穩定、強韌。

- 極致補水,持久鎖潤:運用生物科技保濕因子,構建肌膚內部立體儲水網絡,實現瞬時補水與長效鎖水,令肌膚持續保持水潤飽滿,告別干燥。

- 提亮光澤,改善暗沉:促進肌膚新陳代謝,幫助代謝老廢角質,淡化因干燥和氧化造成的膚色暗啞,使肌膚煥發通透、健康的光采。

- 舒緩維穩,柔嫩膚質:有效舒緩肌膚不適,改善因敏感、環境變化引起的泛紅、粗糙問題,令肌膚觸感日益細膩柔滑。

四、 上市在即,期待與您邂逅

8月5日,這個夏日未央的清新時節,歐瀾精靈系列生物科技面膜將正式登陸各大官方平臺、線下精選門店及授權零售渠道。我們堅信,這款融合了創新生物科技與極致體驗的產品,將成為您護膚routine中不可或缺的煥新力量。

敬請期待,與歐瀾一同探索生物科技帶來的肌膚新生奧秘,開啟專屬于您的清新、強韌、光彩煥發的肌膚未來。讓科技觸摸肌膚,讓美麗源于內在。